仕様を決めよう

仕様を決めよう と言ってもほぼ書籍の通りだけど、1bitに簡略化した為に機能がいくつか減っている。

まずハードの仕様

- レジスタ:Aレジスタ(1bit)、Bレジスタ(1bit)

- ROM:5bit幅×4

- ROMアドレス:0b00 ~ 0b11

- 入力:1bit

- 出力:1bit

まずレジスタだが、当然1bitである。

そして書籍ではキャリーフラグもあり、このフラグを見てアドレスをジャンプするのだが、今回の1bitCPUはレジスタが1bitなのでデータ長も1bitである。ということは…0か1しか表現できない。ということは…ジャンプ先のアドレスは0か1しかない。 これではジャンプ命令の意味がないため、今回はキャリーフラグは見ない。

よってフラグレジスタは実装しない!

次にROMアドレスだが、これは0b00(10進数の0)から0b11(10進数の3)までにした。なぜなら…プログラムカウンタを作るの楽だからである。 さすがに0か1の2アドレスは寂しすぎるし、4アドレスとした。

つぎは命令仕様

- 命令長:5bit(オペコード4bit、オペランド1bit)

オペコードというのは下に書く各種命令のこと。オペランドは下に書くIm:イミディエイトデータのこと。

- 命令の種類:以下に命令を示す。命令名:命令コード:意味という順で列挙する。

| MOV A, Im | 0b0011 | ImをAレジスタに転送する |

| MOV B, Im | 0b0111 | ImをBレジスタに転送する |

| MOV A, B | 0b0001 | BレジスタをAレジスタに転送する |

| MOV B, A | 0b0100 | AレジスタをBレジスタに転送する |

| ADD A, Im | 0b0000 | AレジスタにImを加算する |

| ADD B, Im | 0b0101 | BレジスタにImを加算する |

| IN A | 0b0010 | 入力ポートからAレジスタに転送する |

| IN B | 0b0110 | 入力ポートからBレジスタに転送する |

| OUT A | 0b1001 | Bレジスタから出力ポートへ転送する |

| OUT Im | 0b1011 | Imを出力ポートへ転送する |

| NOP | ADD A, 0 | 何もしない |

あ…あと、加算命令ADDは0+0、0+1、1+0しか出来ない。1bit CPUだから。

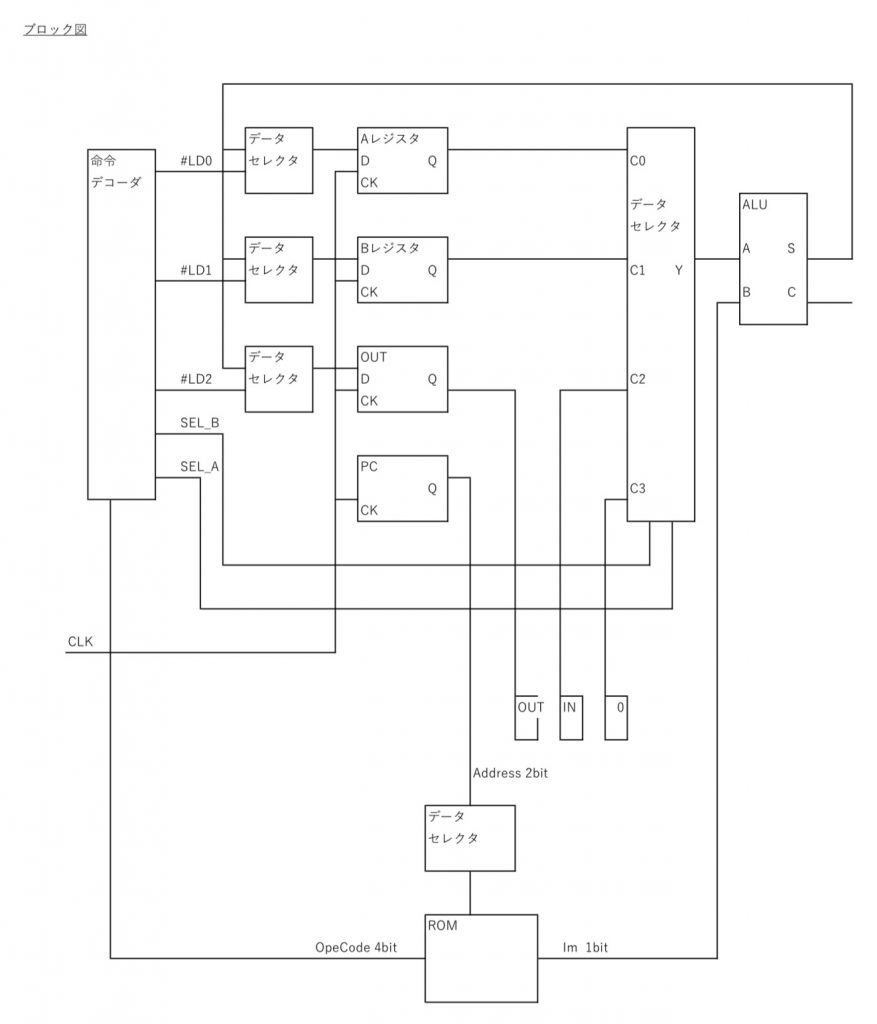

ブロック図

これから作るCPUのイメージ図を作る。かなりお粗末な図だが、なんとなくのイメージはできるかと。